USB2.0 PHY

Overview

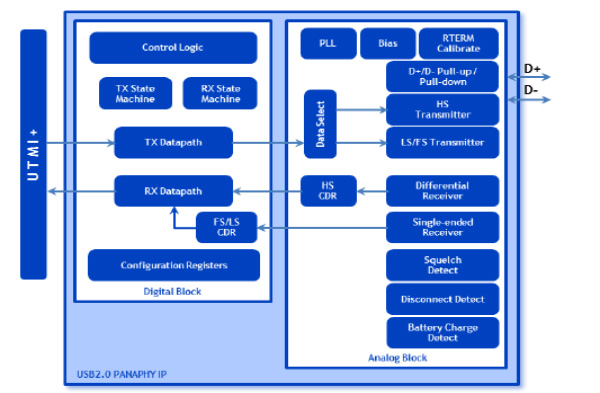

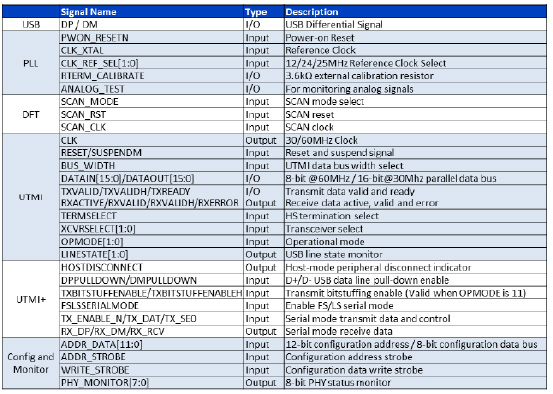

The USB2.0 PHY IP is a complete physical layer (PHY) IP solution designed for low power and peak performance. The USB2.0 IP implements a High-Speed USB 2.0 transceiver for use with either host and device function controllers. Compliant with the UTMI+ level 3 specification, the USB2.0 PHY IP integrates mixed-signal circuits to support High-Speed data rate at 480Mbps and is backward compatible to Full-Speed (12Mbps) and Low-Speed (1.5Mbps) data rates. Targeting mobile and consumer product applications, the USB2.0 PHY IP also supports the supplementary USB Battery Charging specification.

Features

- Fully compliant with USB 2.0 specifications

- Supports the UTMI+ level 3 specifications

- Supports USB Battery Charging

- Supports 480 Mbps High-Speed (HS), 12 Mbps Full-Speed (FS), and 1.5 Mbps Low-Speed (LS) data transmission rates

- Can be configured as host controller or device peripheral

- Utilizes 8-bit interface at 60MHz operation or 16-bit interface at 30MHz operation

- Supports USB 2.0 Test Mode

- Built-in self test mode to validate high-speed, full-speed and low-speed functionality

- Single parallel data clock output with on-chip PLL to generate higher speed serial data clocks

- Selectable input reference clock frequency (12/24/25MHz)

- Available in both 1-port and 2-port configuration