MIPI DPHY-Tx

Overview

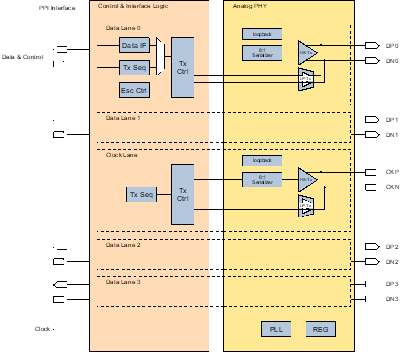

Silicon Library (SLI) MIPI® D-PHY TX IP is a complete PHY solution that is fully compliant to MIPI D-PHY specification version 1.2, enabling easy integration of MIPI® D-PHY interface into low-power modern SoCs. The solution consists of Analog PHY and digital Control and Interface Logic (CIL). PHY is provided as a hard macro supporting high-speed data rates up to 2.5Gbps, while CIL is provided as a synthesizable soft macro. This IP solution can be applied to both MIPI® Camera Serial Interface (CSI-2) and MIPI® Display Serial Interface (DSI) protocols. Both High-Speed (HS) and Low-Power (LP) mode are supported with one Clock Lane and four Data Lanes.

Features

- Compliant with MIPI D-PHY ver1.2

- Supports MIPI standard PHY Protocol Interface (PPI)

- Supports both HS mode (from 80Mbps to 2.5Gbps) and LP mode (up to 10Mbps)

- Supports unidirectional four data lanes

- Supports unidirectional clock lane

- Configurable lanes for either data or clock

- Skew calibration sequence

- 8:1 serializer

- Integrated at-speed BIST(Built-In Self-Test)

- Supports transmitter DC test, IDDQ test

- Programmable analog characteristics

Availability

This IP is available as Silicon proven ‘off-the-shelf’ product in TPSco 65nm. Please download the product brief or contact sales for more detailed information. SLI will accept porting requests from customers.