MIPI D-PHY/LVDS Combo TX IP

Overview

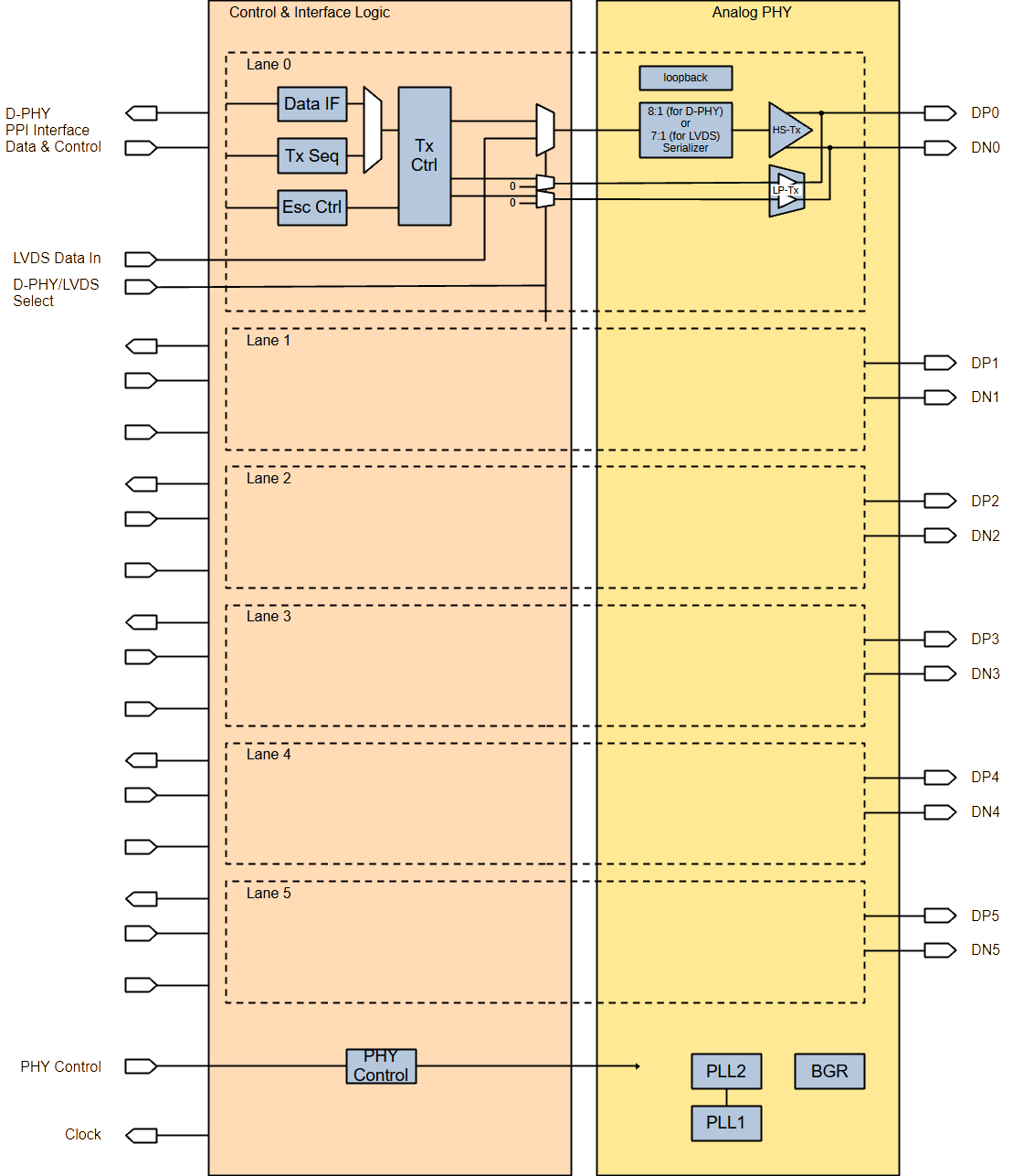

Silicon Library (SLI)’s MIPI D-PHY/LVDS Combo Tx IP solution is compliant with both MIPI D-PHY version 1.2 and LVDS specifications that can be applied to OpenLDI V0.95, which is the best solution to save both the pin counts and die area of modern SoCs. This IP solution is provided as the combination of physical layer (PHY) hard macro and D-PHY Control and Interface Logic (CIL) soft macro. Each of six lanes, supporting a maximum data rate of 1.5 Gbps, can be configured as either data lane or clock lane according to the pin assignment preference. Two PLLs with programmable frequency dividers are included in PHY.

Features

MIPI D-PHY Ver1.2 compliant Tx

- Supports both HS mode (from 80Mbps to 1.5Gbps) and LP mode (up to 10Mbps)

- Each lane can be configured as ether a data lane or a clock lane

- Two PLLs with programmable frequency dividers

- Supports PHY Protocol Interface (PPI)

LVDS compliant Tx

- Supports from 80Mbps to 1.5Gbps data rates

- Supports reduced swing mode

- Applicable to OpenLDI V0.95

- Supports Dual LVDS mode by using two sets of this IP solution

Testability

- At Speed Test by Loopback BIST

- PLL bypass mode

- Analog test

Availability

This IP is available as Silicon proven ‘off-the-shelf’ product in Global Foundries 55nm. Please download the product brief or contact sales for more detailed information. SLI will accept porting requests from customers.