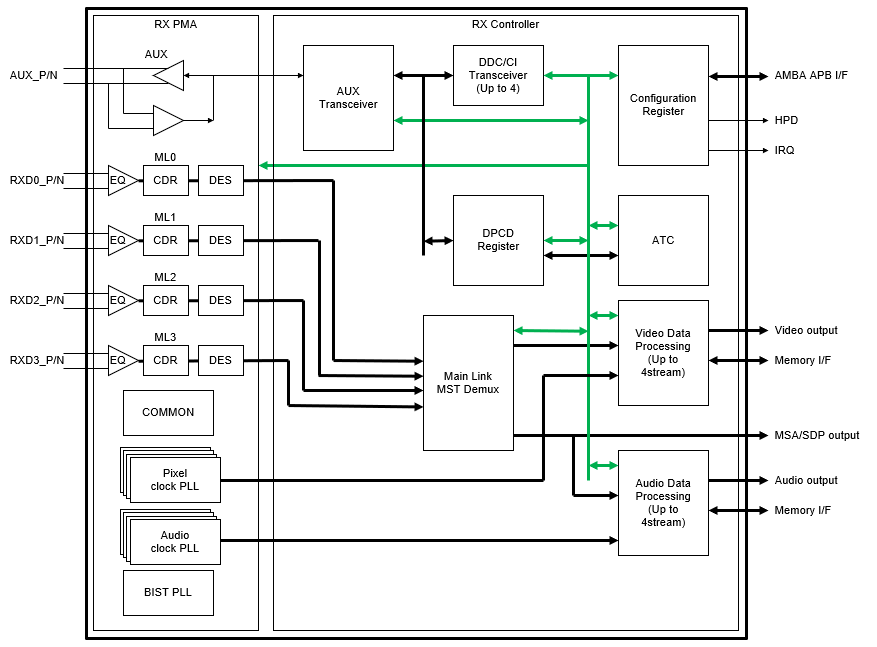

DisplayPort 1.4a / eDP 1.4b RX PHY and Controller IP

Overview

Silicon Library (SLI) DisplayPort (DP) 1.4a / Embedded DisplayPort (eDP) 1.4b RX IP cores provide a comprehensive transmitter solution compliant with VESA DisplayPort 1.4a and Embedded DisplayPort (eDP) 1.4b standards, enabling seamless integration into SoCs for modern multimedia applications. The solution consists of two modules: a physical layer (PHY) and a controller (Link Layer / PCS). The PHY is a hard macro supporting high-speed data rates up to 8.1Gbps (HBR3), while the controller is pprovided as a synthesizable soft macro. In addition to required DisplayPort functionalities, the solution supports optional features including Multi-Stream Transport (MST), Display Stream Compression (DSC), Forward Error Correction (FEC) and HDCP 1.4/2.3 content protections can be added to the configurable controller. SLI’s PHY IPs and Controller IPs work together to deliver the best results with simplified integration although SLI’s PHY and Controller IPs can be offered as independent products.

Features

- Compliant with DisplayPort 1.4a and eDP 1.4b standards

- Composed of 4 main link channels and 1 AUX channel

-

Supports data rates from 1.62Gbps (RBR) to 5.4Gbps (HBR2) or 8.1Gbps (HBR3) per lane

- ⇒ Also Supports all recommend data rates (i.e. 2.16Gbps) defined in eDPv1.4b

- Configurable lane count 1, 2 and 4 lanes

- Integrated 100-ohm termination resistors with common-mode biasing

- Receiver equalizer with adjustable strength

- Programable analog characteristics

- Supports ALPM (Advanced Link Power Management) as option.

- Test features including analog signal monitoring, PLL testing, and BIST (Built-In Self-Test)

Controller Features

- DP version 1.4a / eDP version 1.4b compliant receiver

- Supports SST (Single-Stream Transport)

- Optionally supports MST (Multi-Stream Transport) and MSO (Multi-SST Operation)

Capable of receiving both video and audio packets

- ⇒Supports all digital video output formats (RGB/YCbCr/RAW/Y-only)

- ⇒Supports LPCM audio (up to 8ch) via I2S slave I/F

- I2C (DDC/CI) interface for E-EDID

- Supports HDCP 1.4 / 2.3 (optional)

- Supports DSC and FEC (Rambus Inc) as options

Block diagram

Availability

This PHY IP is available as Silicon proven ‘off-the-shelf’ IP in various major fabs and technology nodes from 28nm to 55nm. Please download the product brief or contact sales for more detailed information. SLI will accept porting requests from customers.